Guía Técnica 74LS83 / 74S283: Sumador Binario de 4 Bits con Acarreo Anticipado74ls283

El Guía Técnica 74LS83 / 74S283: Sumador Binario de 4 Bits con Acarreo Anticipado (74ls283) es un componente electrónico de alta calidad, diseñado para aplicaciones profesionales en decodificadores y sistemas digitales.

Galería

Guía Técnica 74LS83 / 74S283: Sumador Binario de 4 Bits con Acarreo Anticipado

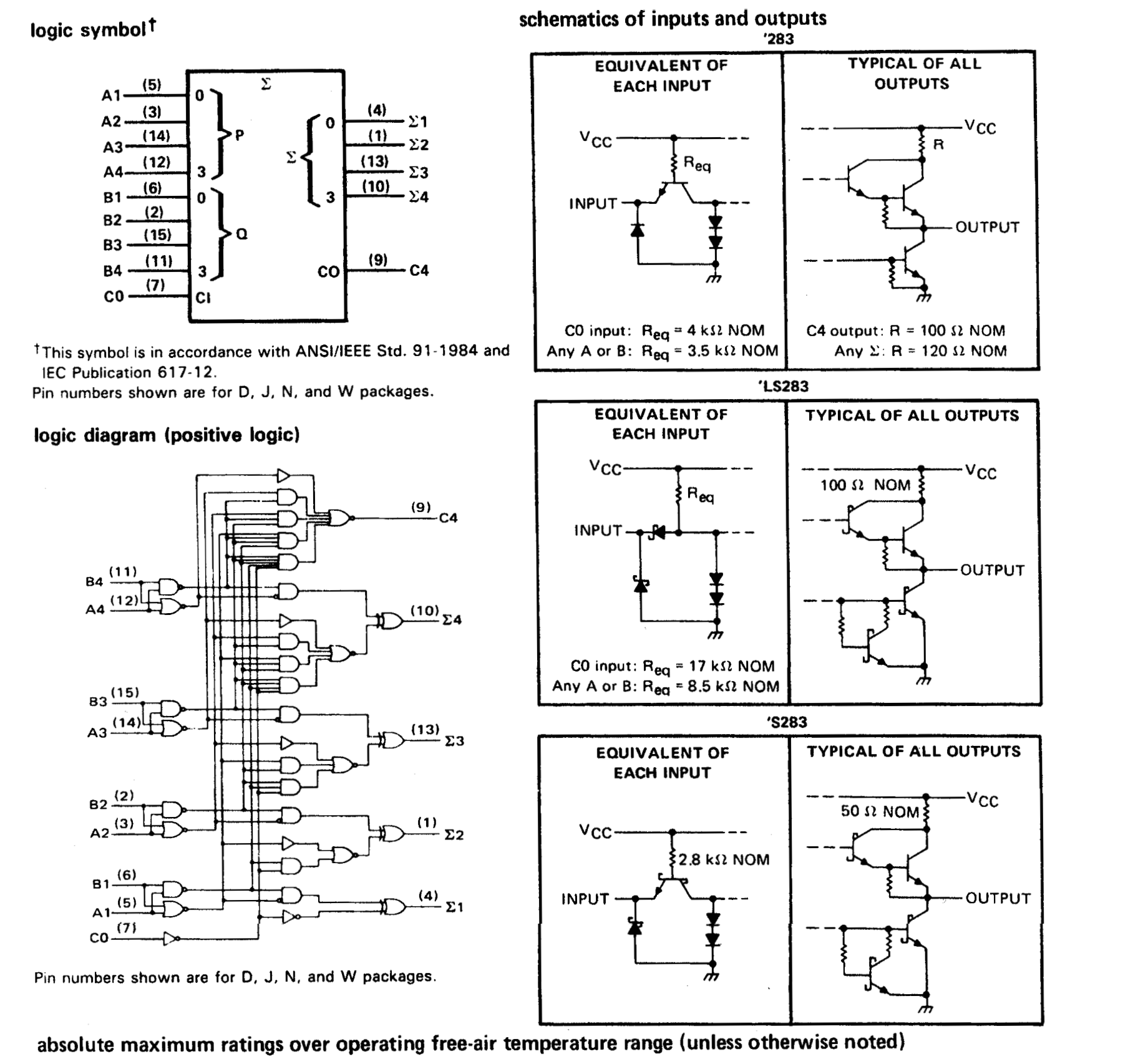

El 74LS83 (y su variante de alta velocidad 74S283) es una pieza fundamental de la arquitectura computacional clásica. No es un simple sumador en cascada; utiliza una topología de Look-Ahead Carry (acarreo anticipado) para mitigar el cuello de botella que supone el retardo de propagación en diseños de aritmética síncrona. Si intentas construir un sumador de 16 bits simplemente encadenando compuertas Full Adder sin esta lógica, acabarás con una latencia de propagación digna de una conexión de dial-up de los 90. Este silicio resuelve la suma completa en un solo ciclo de propagación interna.

⚠️ Límites de Supervivencia

Cualquier intento de alimentar este integrado fuera de los márgenes TTL estándar resultará en la degradación inmediata de las uniones PN.

| Parámetro | Valor Máximo | Unidad |

|---|---|---|

| Tensión de Alimentación ($V_{CC}$) | 7.0 | V |

| Tensión de Entrada ($V_{I}$) | 5.5 (LS) / 7.0 (S) | V |

| Temperatura de Operación | 0 a 70 | °C |

| Corriente de Salida (High) | -400 | µA |

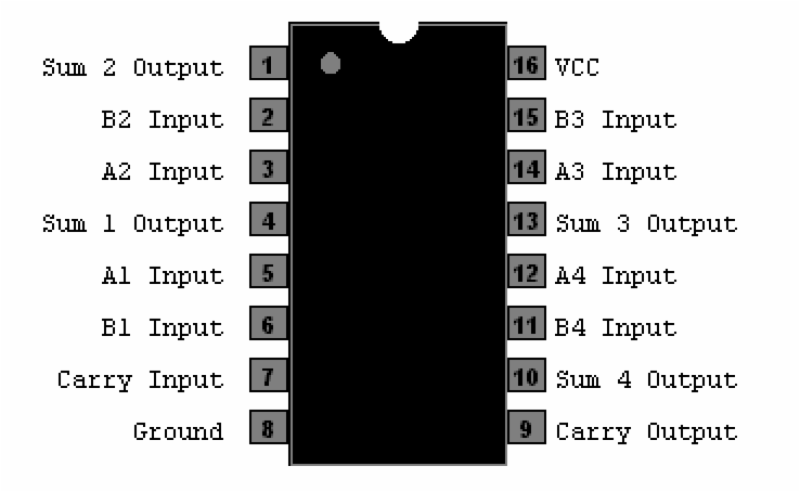

Pinout y Referencia Física

El esquema proporciona la lógica interna y la disposición de pines para el encapsulado DIP de 16 terminales.

| Pin | Nombre | Función |

|---|---|---|

| 1, 3, 14, 12 | A1, A2, A3, A4 | Entradas de Datos Operando A (LSB a MSB) |

| 2, 6, 15, 11 | B1, B2, B3, B4 | Entradas de Datos Operando B (LSB a MSB) |

| 4, 1, 13, 10 | $\Sigma 1, \Sigma 2, \Sigma 3, \Sigma 4$ | Salidas de la Suma Binaria |

| 7 | $C_0$ | Entrada de Acarreo (Carry In) |

| 9 | $C_4$ | Salida de Acarreo Final (Carry Out) |

| 5 | $V_{CC}$ | Alimentación (+5V Típico) |

| 13 | GND | Tierra |

Ingeniería Aplicada: Análisis de Implementación

El diagrama lógico revela la elegancia del Acarreo Anticipado. En lugar de esperar a que cada bit genere un acarreo para el siguiente ($C_{n+1}$), el 74LS83 calcula el estado del acarreo final basándose únicamente en las entradas iniciales. Esto reduce drásticamente el $t_{pd}$ (tiempo de retardo de propagación).

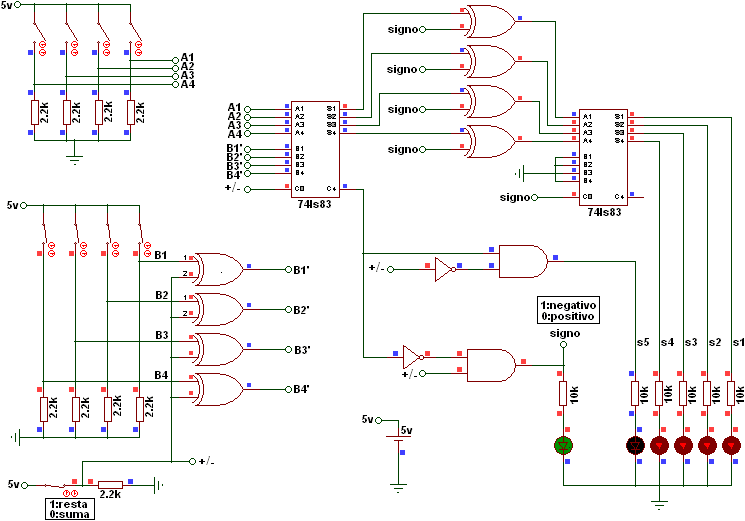

En el circuito de aplicación suministrado, observamos un Calculador Aritmético de Complemento a 2. El diseñador ha implementado una unidad que puede sumar o restar basándose en una señal de control externa.

- Lógica de Resta: Utiliza compuertas XOR para invertir los bits del operando B cuando la señal

+/-está en alto. Al inyectar esa misma señal en el acarreo inicial ($C_0$), se completa la operación de complemento a 2: $$A + (\bar{B} + 1) = A - B$$. - Gestión de Signo: El circuito incluye una etapa de post-procesamiento para determinar si el resultado es negativo, utilizando un segundo 74LS83 para re-convertir el número si el bit de signo está activo. Si el diseño omite esta etapa, los números negativos simplemente se verían como valores absurdos en binario puro.

Este detalle técnico es donde la mayoría de los entusiastas fallan. Las entradas del 74LS83 tienen una resistencia equivalente ($R_{in}$) de 3.5 k$\Omega$ a 8.5 k$\Omega$. Ignorar las corrientes de fuga o no usar resistencias de pull-down adecuadas (como las de 2.2k que se ven en el esquema de usuario) es la receta perfecta para obtener niveles lógicos indeterminados y un comportamiento errático que culparás al "chip defectuoso" cuando el error está en tu protoboard.

Veredicto BySMax

El 74LS83 sigue siendo el estándar de oro para enseñanza de arquitectura y prototipado rápido de ALUs discretas. Su lógica de acarreo anticipado lo separa de la basura técnica de baja velocidad. Es una pieza de ingeniería robusta, siempre que no seas lo suficientemente descuidado como para olvidar que los niveles TTL son intolerantes al ruido.

¿Deseas que profundice en el cálculo del tiempo de propagación total ($t_{pd}$) para una cascada de 16 bits con estos componentes?

Tutoriales

Aplicaciones

Estas aplicaciones muestran la versatilidad del componente en diferentes áreas de la electrónica.

Especificaciones Técnicas

Información General

74ls283

Información Adicional

El guía técnica 74ls83 / 74s283: sumador binario de 4 bits con acarreo anticipado es un componente fundamental en la categoría de decodificadores. Su diseño y características lo hacen ideal para una amplia gama de aplicaciones en electrónica digital.

Proyectos Relacionados con Guía Técnica 74LS83 / 74S283: Sumador Binario de 4 Bits con Acarreo Anticipado

- No posts found.

Haz clic para cargar comentarios